電子機器の進化は、常に「より小さく、より速く、より高効率に」という命題との戦いでした。

スマートフォン、ウェアラブルデバイス、そしてAI処理を担うエッジデバイスにおいて、従来の基板表面に部品を並べる表面実装技術(SMT)は、物理的な限界を迎えつつあります。

そこで注目されているのが、基板の内部にICや受動部品を埋め込む部品内蔵基板技術です。

この技術は単なる省スペース化の手法に留まらず、回路設計のパラダイムシフトを引き起こしています。

本記事では、部品内蔵基板、特にICを埋め込むことで得られるメリットを、専門的な視点から徹底的に解説します。

部品内蔵基板の定義と市場背景

部品内蔵基板とは何か?

部品内蔵基板とは、プリント配線板の絶縁層の内部に、IC(集積回路)やコンデンサ、抵抗などの電子部品を配置し、樹脂等で封止した基板を指します。

従来の基板が表面(Top/Bottom層)にのみ部品を搭載していたのに対し、基板そのものを3次元の実装空間として活用するのが最大の特徴です。

一般的には、コア材に設けたキャビティ(穴)に部品を配置する手法や、ビルドアップ層の中に部品を埋め込む手法が採用されます。

これにより、基板表面は他の部品やコネクタのために解放され、これまでにない高密度実装が可能となります。

なぜ今、ICの埋め込みが求められているのか?

背景にあるのは、5G/6G通信の普及と、デバイスのさらなる多機能化です。通信速度が向上すればするほど、信号の減衰やノイズの問題は深刻化します。

従来の表面実装では、ICから基板を通って他の部品へ至るまでの配線長がボトルネックとなり、高速信号の品質を維持することが困難になってきました。

また、AI搭載型ウェアラブルデバイスのように、人間の身体に違和感なく装着できるサイズを実現するためには、基板サイズを数割単位で削減する必要があります。

部品内蔵基板は、これらの「物理的限界」と「電気的限界」を同時に突破するための切り札として、2026年現在の電子設計において不可欠な技術となっています。

メリット1:実装面積の劇的な削減(圧倒的な小型化)

3次元実装によるフットプリントの最小化

部品内蔵基板を導入する最大の直接的なメリットは、基板表面の専有面積を劇的に削減できることです。

従来の表面実装では、ICを配置した場所の裏面や周囲には一定の禁止領域(Keep-out zone)が必要でしたが、内蔵化によってその制約が解消されます。

ICを基板の内部に「沈める」ことで、その真上の表面空間を別の部品(例えばセンサーやスイッチ、アンテナなど)の実装に充てることが可能になります。

これにより、従来の設計と比較して、基板全体のフットプリントを30パーセントから50パーセント程度削減できるケースも珍しくありません。

デバイスの薄型化・高密度化への寄与

部品を内蔵することは、単に面積を削るだけでなく、製品全体の薄型化にも寄与します。

通常、ICをパッケージ(QFPやBGA)として表面に実装すると、そのパッケージの高さ分だけ筐体の厚みが必要になります。

しかし、ベアダイ(パッケージング前のシリコンチップ)を直接基板内に埋め込むベアダイ内蔵技術を用いれば、パッケージ分の厚みを完全に排除できます。

多層基板の厚み自体はわずかに増すものの、トータルでのモジュール厚は大幅に薄くなり、極限の薄さが求められるクレジットカード型デバイスや医療用パッチ型センサーの実現を後押しします。

メリット2:電気的特性の飛躍的向上(シグナルインテグリティ)

配線長の短縮による寄生インダクタンスの低減

電気設計エンジニアにとって、部品内蔵の真の価値はシグナルインテグリティ(信号品質)の向上にあります。

ICを基板内部に配置することで、ICの端子から他の部品(特にデカップリングコンデンサ)までの距離を最短化できます。

電気工学の観点では、配線長 $l$ が短くなることは、寄生インダクタンス $L$ の低減に直結します。

インダクタンスが低減されることで、電源供給網(PDN)のインピーダンスが下がり、高速動作時でも電圧ドロップ(IR Drop)や電源ノイズが抑制されます。これは、1GHzを超える高周波で動作するプロセッサにおいて、安定動作を担保するための決定的なアドバンテージとなります。

高周波特性の改善とノイズ抑制効果

部品を基板内部に埋め込み、周囲をグラウンド層(GND層)で囲むことで、優れた電磁遮蔽(シールド)効果が得られます。これにより、外部からの電磁干渉(EMI)を防ぐだけでなく、IC自体が発生させる不要放射(EMS)も基板内部で封じ込めることが可能になります。

特に5G/6Gで利用されるミリ波帯の設計では、配線のわずかな曲がりやビア(Via)による信号反射が致命的なロスとなります。内蔵基板では、フリップチップ接続等を用いてビアを介さずに最短で内層配線へ接続できるため、インピーダンス整合が取りやすく、極めてクリーンな信号伝送を実現できます。

メリット3:熱マネジメントと信頼性の強化

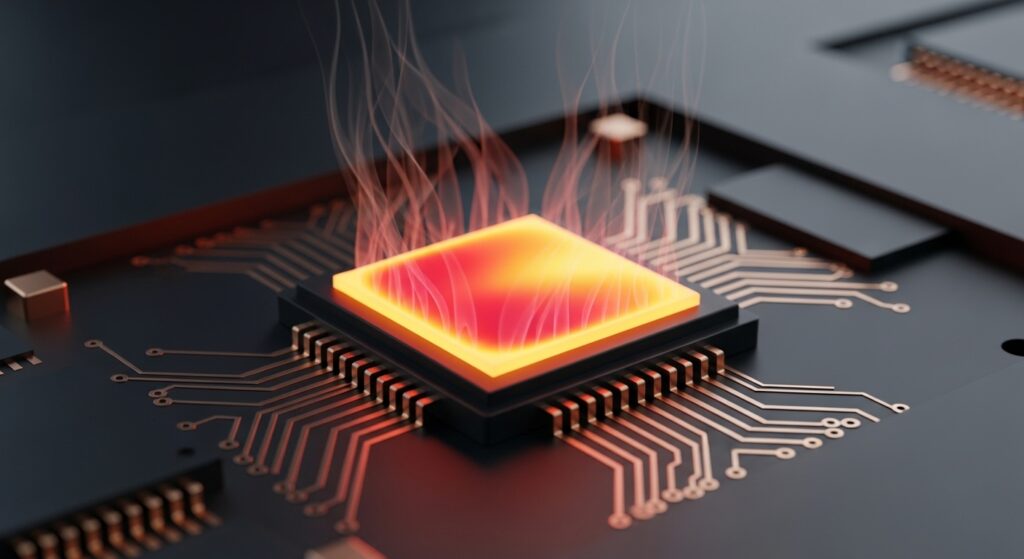

基板内部の熱拡散経路の最適化

ICの高機能化に伴い、発熱対策は設計上の大きな課題です。表面実装の場合、熱は主に基板表面の空気中へ放熱されるか、基板の銅箔を伝って広がりますが、空気の熱伝導率は極めて低いため、効率が良くありません。

部品を内蔵し、サーマルビア(放熱用の穴)や高熱伝導性樹脂で周囲を固めることで、基板全体を巨大なヒートシンクとして活用できるようになります。チップから発生した熱を多層基板の各層にある銅箔面へダイレクトに逃がすことができるため、局所的なホットスポットの発生を抑え、デバイスの動作安定性を向上させることが可能です。

部品保護と機械的強度の向上

基板内部に封止された部品は、外部の過酷な環境(湿度、酸素、物理的な衝撃)から物理的に保護されます。表面実装部品のように、落下衝撃でハンダ接合部にクラックが入ったり、湿気によって腐食が進んだりするリスクを大幅に低減できます。

また、樹脂で一体成型されるため、基板全体の剛性が向上します。これは、常に振動にさらされる車載用電子機器や、過酷な現場で使用される産業用ロボットの制御基板において、長期的な信頼性を担保するための強力な武器となります。

導入にあたっての課題と解決策(コスト・検査・歩留まり)

ここまではメリットを強調してきましたが、プロの視点として、導入の障壁となる課題とその対策についても触れておく必要があります。

KGD(Known Good Die)確保の重要性

部品を基板の中に埋め込んでしまうと、後から「ハンダ付けをやり直す(リワーク)」ことは不可能です。

もし内蔵したICが不良品だった場合、基板全体を廃棄しなければなりません。

このリスクを回避するために不可欠なのが、KGD(良品であることが保証された裸チップ)の確保です。

半導体メーカーと協力し、ウェハレベルでの厳格なテストをパスしたチップを使用することが、歩留まり向上の絶対条件となります。

テスト・検査プロセスの進化

埋め込まれた部品は目視で確認できないため、従来の光学検査(AOI)は通用しません。

そのため、X線検査装置による非破壊検査や、境界スキャン(Boundary Scan)技術を用いた電気的テストが重要になります。

幸いなことに、2026年現在はAIを用いたX線画像解析技術が飛躍的に進化しており、微細な接合不良も自動で高精度に検出できるようになっています。

設計段階からテスト容易化設計(DFT)を組み込むことで、量産時の歩留まりリスクは十分にコントロール可能なレベルに達しています。

まとめ:部品内蔵基板が切り拓く電子機器の未来

部品内蔵基板へのIC埋め込みは、単なる実装技術の選択肢の一つではありません。それは、プロダクトデザインの自由度を解放し、電気的性能を極限まで引き出し、信頼性を高めるための総合的な戦略です。

小型化・高機能化への要求が止まることのない現代において、この技術を使いこなせるかどうかは、製品の競争力を左右する重要なファクターとなります。コストや歩留まりといった課題は、設計手法の最適化とサプライチェーンとの連携によって克服されつつあります。

あなたの次なるプロジェクトで、部品内蔵基板という選択肢を検討してみてはいかがでしょうか。それは、これまでの設計の常識を覆し、新たな価値を創造する第一歩になるはずです。

参考・推奨リンク

- 一般社団法人 日本電子回路工業会 (JPCA):部品内蔵基板の規格化(EB01規格など)を推進している権威ある団体です。

- IEEE Xplore:最新の3D実装技術や電気的特性に関する学術論文を確認するための国際的なプラットフォームです。