電子機器の製造において、基板実装(SMT: Surface Mount Technology)は最も重要かつ繊細な工程の一つです。

設計図の上では完璧であっても、実際の製造現場では、はんだの乗り具合や部品の配置位置、加熱温度のわずかな差が、製品の動作不良という致命的な結果を招くことがあります。

特に部品の小型化が進む現代では、肉眼では確認できないレベルの微細な不良が発生しやすく、多くの製造担当者や開発者が歩留まり(良品率)の改善に頭を悩ませています。この記事では、基板実装の現場で頻発する代表的な失敗例を挙げ、その発生メカニズムと具体的な対策を詳細に解説します。この記事を読むことで、トラブルの根本原因を理解し、製造工程の最適化や設計段階でのリスク回避ができるようになるでしょう。

基板実装の失敗とは:言葉の定義と背景

基板実装における失敗とは、一般に「実装不良」と呼ばれます。これは、プリント配線板に電子部品を固定し、電気的な通り道を形成するプロセスにおいて、意図した通りの接合が得られない状態を指します。

なぜ失敗の対策が重要なのか

- コストへの影響 不良が発生すると、基板を廃棄(スクラップ)するか、熟練の作業員が手作業で修正(リワーク)する必要があります。これらは多大な人件費と材料費のロスを生みます。

- 信頼性の低下 出荷時の検査をすり抜けた微細な不良が、市場に出てから数ヶ月後に故障を招くケースがあります。これは企業のブランドイメージを大きく損なうリスクとなります。

- 製造サイクルの短縮 不具合の原因特定に時間がかかると、量産開始のスケジュールが遅れ、市場投入のタイミングを逃してしまいます。

現代の製造現場では、失敗を「後から見つける」のではなく、仕組みとして「発生させない」ことが求められています。

具体的な仕組み:主要な不良の発生メカニズム

基板実装でよくある失敗には、物理的な法則や材料の特性に起因する明確なメカニズムがあります。代表的な3つの例を詳しく解説します。

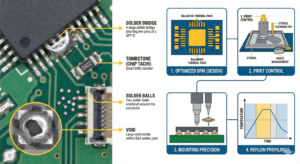

1. はんだブリッジ(ショート)

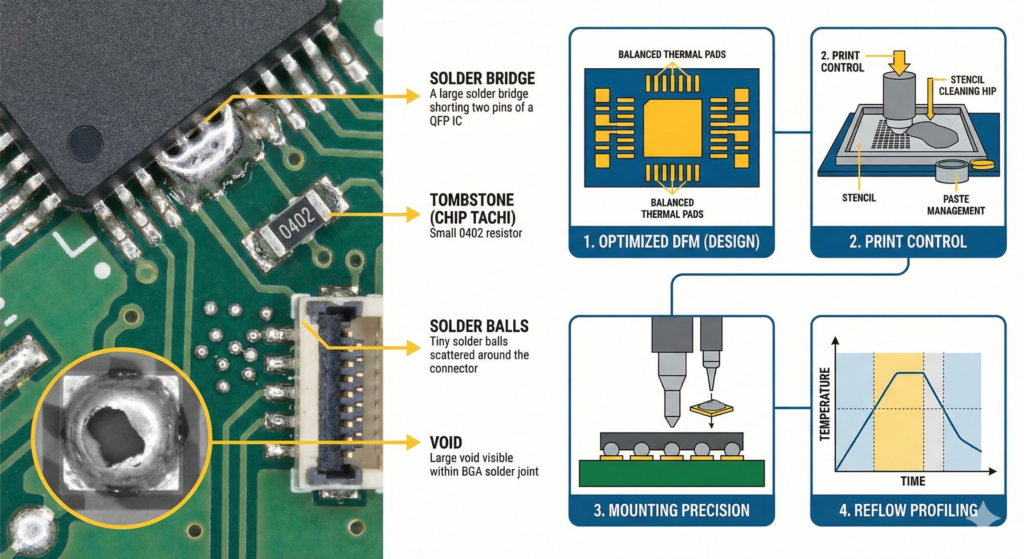

はんだブリッジとは、隣り合う端子同士がはんだによって繋がってしまい、電気的にショートする現象です。 発生の仕組み: はんだ印刷工程で、クリームはんだ(ソルダーペースト)が必要以上に多く塗布されたり、印刷位置がわずかにズレたりすることが引き金となります。リフロー炉で加熱され、はんだが液体になった際、表面張力によって隣のはんだと合体してしまいます。特に、ICのピン間隔が狭い「ファインピッチ部品」で発生しやすい不良です。

2. チップ立ち(マンハッタン現象・トンボ現象)

抵抗やコンデンサなどの小さなチップ部品が、片側だけ浮き上がって垂直に立ってしまう現象です。 発生の仕組み: はんだが溶ける際、部品の両端にかかる「濡れ力(はんだが金属に馴染もうとする力)」のバランスが崩れることで発生します。例えば、片方のパッド(基板の接続部)が大きな配線層に繋がっていて熱が逃げやすい場合、もう片方のはんだが先に溶けます。先に溶けた側のはんだが部品を引っ張り上げる力に、まだ溶けていない側の重みが負けてしまい、部品が立ち上がります。

3. はんだボール(はんだの飛散)

本来はんだが付着すべきでない場所に、小さな球状のはんだが散らばる現象です。 発生の仕組み: 加熱の過程で、クリームはんだに含まれる「フラックス(酸化膜を除去する薬剤)」が急激に沸騰し、周囲にはんだの微粒子を弾き飛ばすことで起こります。また、はんだ印刷の際にメタルマスクの裏側に付着した余分なはんだが、次の基板に転写されることも原因となります。これらは後々、基板内を移動して予期せぬショートを引き起こす原因となります。

作業の具体的な流れ:失敗を防ぐための5ステップ

不良を未然に防ぐには、各工程で適切な管理を行う必要があります。具体的な作業の流れに沿って対策を見ていきましょう。

ステップ1:設計(DFM)段階での対策

すべては設計から始まります。これをDFM(Design for Manufacturing:製造を考慮した設計)と呼びます。

- サーマルリリーフの作成:熱が逃げやすい大きなパターンと部品の間に細い配線を入れ、両端の熱バランスを整えます(チップ立ち防止)。

- 適切なレジスト設計:隣り合うパッドの間に、はんだを弾く「ソルダーレジスト」のダムを設け、物理的にブリッジを防ぎます。

ステップ2:はんだ印刷工程の最適化

印刷機での管理が実装品質の7割を決めると言われています。

- メタルマスクの清掃:定期的な裏面清掃を自動化し、はんだの滲みを防ぎます。

- はんだの温度管理:冷蔵保管されていたクリームはんだを十分に常温に戻し、撹拌(かくはん)して粘度を安定させます。

ステップ3:マウンティング(部品配置)の精度維持

マウンター(部品を載せる機械)の吸着ミスや配置ズレを抑えます。

- ノズルの点検:部品を吸い上げるノズルに汚れや摩耗がないかチェックします。

- 認識カメラの校正:部品の形状を正しく認識し、ミクロン単位で位置を補正できるようにメンテナンスを行います。

ステップ4:リフロー(加熱)条件の設定

加熱の「温度プロファイル」を部品や基板の構成に合わせて調整します。

- 予熱時間の確保:本加熱の前に基板全体を均一に温め、フラックスを十分に活性化させます。これにより、はんだボールの発生や部品の立ちを抑えます。

- 酸素濃度の管理:窒素(N2)リフロー炉を使用し、酸化を防ぐことで、はんだの濡れ性を向上させます。

ステップ5:検査とフィードバック

SPI(はんだ印刷検査機)やAOI(自動光学検査機)を導入し、不具合をデータ化します。

- リアルタイム補正:印刷機でズレが発生していることをSPIが検知したら、即座に印刷機へデータを戻して位置を修正する「M2M(Machine to Machine)」連携を活用します。

最新の技術トレンドや将来性:AIと自動化による「ゼロ不良」

基板実装の失敗対策は、現在デジタルテクノロジーによって劇的な進化を遂げています。

AIによる高度な判定と学習

従来の自動検査機では、影の入り方などで良品を不良と誤診する「過判定」が課題でした。最新のシステムではAI(ディープラーニング)が導入され、膨大な画像データから「真の不良」のみを高い精度で判別できるようになっています。これにより、人間による再確認の手間が大幅に削減されています。

スマートファクトリーとデジタルツイン

工場全体の稼働状況をデジタル空間上に再現し、シミュレーションを行う技術です。製造前に「この基板レイアウトではチップ立ちが起きやすい」という予測を立て、事前に対策を講じることが可能になりつつあります。

低温はんだ技術の進化

熱に弱い部品の故障を防ぐため、従来よりも低い温度で溶けるはんだの採用が広がっています。これにより、リフロー炉のエネルギー削減と部品へのダメージ回避を同時に実現しています。

よくある質問(FAQ)

Q1:チップ立ちが特定の部品で多発します。何から確認すべきですか?

まずは基板設計を確認してください。部品の両端に繋がる配線の太さが極端に違わないでしょうか。設計に問題がない場合は、リフロー炉の予熱時間を少し長めに設定し、基板全体の温度差を小さくしてみてください。

Q2:はんだブリッジは手作業で直せますか?

はい、フラックスとはんだごて、または「吸取線」を使って修正可能です。ただし、ファインピッチICの場合、手作業による加熱が部品にダメージを与える可能性があるため、リワーク専用の装置(リワークステーション)の使用をおすすめします。

Q3:はんだボールが発生しても、機能試験を通れば出荷して良いですか?

おすすめしません。はんだボールは基板上で固定されていない場合が多く、出荷後の振動や湿気によって移動し、後にショートを引き起こす「時限爆弾」になります。徹底的な洗浄か、印刷工程の見直しが必要です。

Q4:SPI(印刷検査機)は導入すべきですか?

はい。実装不良の約7割が印刷工程に起因するため、マウンターで部品を載せる前に印刷ミスを見つけることで、部品代の無駄を省き、修正コストを劇的に下げることができます。

まとめ

基板実装における失敗は、単なる「運」や「機械の不調」ではなく、熱学や流体力学、材料工学に基づいた結果として現れます。

はんだブリッジ、チップ立ち、はんだボールといった代表的な不良には、それぞれ印刷管理、熱バランスの適正化、設計の見直しといった明確な処方箋が存在します。最新のAI検査やM2M連携といったテクノロジーを取り入れつつ、まずは基本となるDFM(製造を考慮した設計)と温度プロファイルの管理を徹底することが、高品質なモノづくりの第一歩です。

失敗を恐れるのではなく、失敗のメカニズムを理解して先回りして対策を打つ。その積み重ねが、次世代の高度な電子機器製造を支える力となります。