高周波基板設計の世界へようこそ。

現代の電子機器において、5G通信、高速データ伝送、自動運転システムなどの普及に伴い、高周波回路の重要性はかつてないほど高まっています。

低周波の回路設計では無視できていたわずかな配線の長さや幅、隣接する配線との距離が、高周波の世界では致命的なノイズや信号の劣化を引き起こします。

設計者の皆様の中には、シミュレーションでは問題なかったのに、実機を製作すると期待した性能が出ない、あるいは不要輻射(EMI)が基準を超えてしまうといった悩みを抱えている方も多いのではないでしょうか。

この記事では、高周波基板設計におけるノイズ対策の核心であるパターン配置と注意点について、初心者から中級者までが実務で活用できるレベルまで徹底的に解説します。

この記事を読み終える頃には、目に見えない電磁波をコントロールし、安定した高品質な基板を設計するための具体的な指針が身についているはずです。

高周波基板設計の定義と背景:なぜ今、設計技術が重要なのか

高周波基板とは何か

一般的に、信号の周波数が数百MHz(メガヘルツ)から数GHz(ギガヘルツ)以上に達する回路を扱う基板を高周波基板と呼びます。

しかし、デジタル回路の高速化が進んだ現代では、クロック周波数そのものが低くても、信号の立ち上がり時間(ライズタイム)が速ければ、それは高周波成分を含んでいると見なす必要があります。

高周波設計の本質は、電気信号を単なる電流の流れとしてではなく、電磁波の伝搬として捉えることにあります。

なぜ設計が重要なのか:3つのリスク

- 信号完全性(Signal Integrity: SI)の低下配線での反射や減衰により、送信したデータが受信側で正しく認識できなくなる現象です。波形が崩れることでビットエラーが発生し、通信速度の低下やシステムのフリーズを招きます。

- 電磁両立性(Electromagnetic Compatibility: EMC)の問題基板そのものがアンテナのように動作し、不要な電磁波を放射(EMI)したり、外部からのノイズによって誤動作(EMS)したりする問題です。各国の規制(VCCI、FCCなど)をクリアできなければ、製品として販売することはできません。

- 電源完全性(Power Integrity: PI)の悪化高速なスイッチング動作に伴い、電源電圧が不安定になる現象です。これにより回路全体の動作が不安定になり、高周波ノイズの源となります。

これらのリスクを回避するためには、従来の基板設計の常識を捨て、高周波特有の物理現象に基づいたパターン設計が不可欠なのです。

高周波信号が伝わる仕組み:電磁波の振る舞いを理解する

高周波回路を設計する上で、避けては通れない物理現象がいくつかあります。

これらを視覚的にイメージできるように詳細に解説します。

インピーダンス整合と反射のメカニズム

高周波信号が配線を伝わる際、配線のインピーダンス(交流における抵抗のようなもの)が変化する箇所があると、信号の一部が送信元に跳ね返ってしまいます。

これが反射です。

反射を防ぐためには、送り出し側(ソース)、伝送線路(配線)、受け取り側(ロード)のすべてのインピーダンスを一致させる必要があります。

これをインピーダンス整合と呼びます。

一般的には50Ω(オーム)に設定されることが多いです。

リターンパス(帰路)の重要性

電流は必ず行って帰ってきます。高周波において、帰りの電流(リターン電流)は、往路の配線の直下にあるグラウンド面を流路として選びます。

これは、往路と復路のループ面積を最小にして、エネルギーを最小限に抑えようとする性質があるためです。

もしグラウンド面にスリット(切れ目)があり、リターン電流が迂回せざるを得なくなると、ループ面積が拡大し、大きなインダクタンスが発生します。

これがノイズ放射の最大の原因となります。

皮膚効果(スキンエフェクト)

周波数が高くなると、電流は導体の表面付近に集中して流れるようになります。

これを皮膚効果と呼びます。

例えば、銅箔の厚みが十分に合っても、実際に電流が流れているのは表面の数μm(マイクロメートル)だけという状況が起こります。

これにより実効的な抵抗値が増大し、信号の減衰(挿入損失)を引き起こします。

誘電損失(Dielectric Loss)

基板材料(絶縁体)の中を電磁波が通る際、絶縁体内の分子が激しく振動し、エネルギーが熱として失われる現象です。

周波数が高いほど、また基板の誘電正接(tanδ)が大きいほど損失は激しくなります。

作業の具体的な流れ:ステップバイステップで進める高周波設計

高周波基板の設計は、配置が終わってから配線を考えるのではなく、層構成の段階から勝負が始まっています。

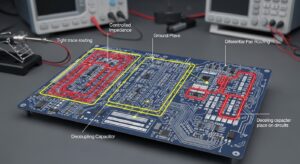

ステップ1:層構成(スタックアップ)の決定

まず、インピーダンスをコントロールするために必要な基板の層構成を決定します。

- 信号層とグラウンド層を隣接させる。

- 誘電体の厚み(h)と、使用する素材の比誘電率(εr)を確認する。

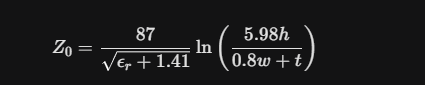

- 特性インピーダンス $Z_0$ を計算し、配線幅を決定する。

マイクロストリップライン(表面配線)の場合、簡易的な計算式は以下のようになります。

ここで、wは配線幅、tは銅箔厚です。実際にはCADのシミュレーターを使用して精密に算出します。

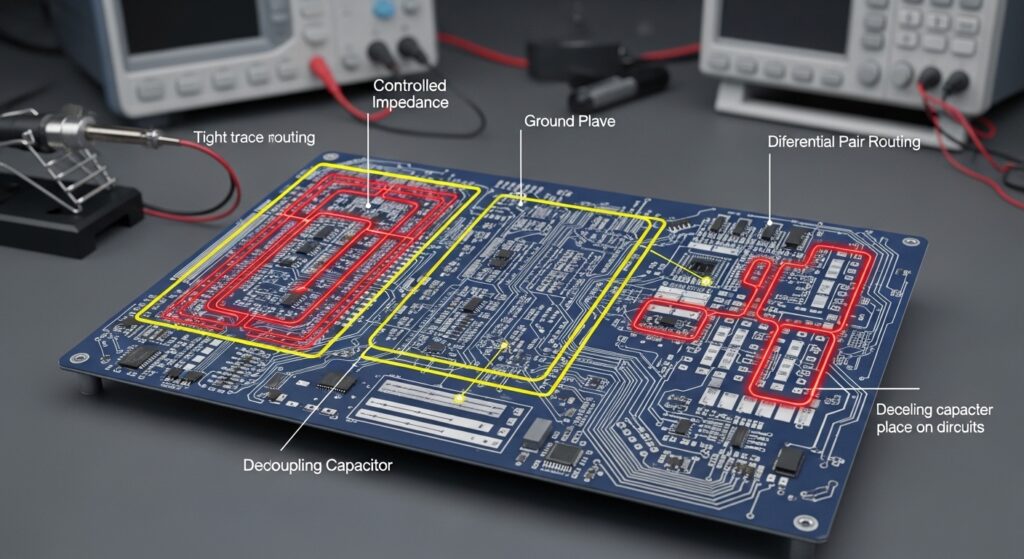

ステップ2:コンポーネントの配置(レイアウト)

部品配置は、信号の流れを最短にすることを最優先します。

- 高周波部品(IC、フィルタ、コネクタ)を中心に配置し、その周辺に関連部品を固める。

- アナログ回路とデジタル回路を物理的に分離し、互いの干渉を防ぐ。

- バイパスコンデンサは、ICの電源ピンの直近に配置し、リード線や配線のインダクタンスを最小化する。

ステップ3:パターンの配線(ルーティング)

いよいよ配線です。ここでは以下のルールを厳守します。

- 直角に曲げない:配線の角は45度にするか、丸みを持たせます。直角部分は配線幅が変化したのと同等の効果(静電容量の増加)を生み、インピーダンスの不連続点となります。

- ビア(Via)の使用を最小限にする:層間を移動するビアは、それ自体が寄生インダクタンスを持ち、高周波信号を劣化させます。どうしても必要な場合は、信号ビアの隣にリターンパス用のグラウンドビアを配置(ステッチングビア)します。

- 差動配線の等長化:高速信号を2本のペアで送る差動配線では、2本の長さを厳密に合わせ、極限まで並行に走らせます。

ステップ4:グラウンドと電源の設計

グラウンドは、高周波設計における命綱です。

- 広大なグラウンドプレーン(面)を確保する:メッシュ状にはせず、ベタ銅で構成します。

- 異種グラウンドの分離と結合:アナロググラウンドとデジタルグラウンドを分離する場合は、一点で結合するか、高周波的に結合させるための工夫が必要です。

ステップ5:検図とシミュレーション

設計が終わったら、DRC(デザインルールチェック)だけでなく、シミュレーションツールを用いて波形解析を行います。

反射の有無、クロストーク(隣接配線からのノイズ転移)が許容範囲内かを確認し、必要に応じてパターンを微調整します。

パターン配置における具体的な注意点とノイズ対策テクニック

ここでは、より踏み込んだテクニックを紹介します。

クロストークの防止(3Wルールの適用)

隣接する配線同士が干渉し合うクロストークを防ぐため、配線間隔を配線幅の3倍以上空けるという「3Wルール」が推奨されます。

特に高電圧な信号や、非常に高速なクロック線については、さらに距離を離すか、間にグラウンドガード(シールド配線)を配置することを検討します。

信号のアイソレーション

入力信号と出力信号、あるいは微弱な受信信号と強力な送信信号が近くにあると、結合して発振や感度低下の原因になります。

これを防ぐために、基板にスリットを入れたり、金属製のシールドケースで物理的に遮蔽したりする手法が取られます。

電源デカップリングの最適化

高周波ICは瞬間的に大きな電流を消費します。これに応えるのがデカップリングコンデンサの役割です。

容量の異なるコンデンサ(例えば1μFと0.01μF)を並列に配置することで、広い周波数帯域でインピーダンスを低く保つことができます。

この際、小さい容量のコンデンサをよりICのピンに近い側に配置するのが鉄則です。

| 対策項目 | 具体的な手法 | 期待できる効果 |

| 反射対策 | 終端抵抗(ダンピング抵抗)の挿入 | 波形のオーバーシュート、アンダーシュートの抑制 |

| EMI対策 | 基板端からの配線後退(20Hルール) | 基板エッジからの不要輻射の低減 |

| 共振対策 | 多点グラウンド接続 | 特定周波数での基板全体の共振防止 |

最新の技術トレンドや将来性

高周波基板設計の分野は、今まさに大きな変革期にあります。

ミリ波帯(30GHz〜)への対応

6G通信や高精度レーダーの開発により、ミリ波と呼ばれる極めて高い周波数が使われ始めています。

この領域では、従来のFR-4基板(一般的なガラスエポキシ基板)は損失が大きすぎて使用できず、フッ素樹脂(テフロン)やセラミックなどの特殊な低損失基板材料が主流となっています。

AiP(Antenna in Package)技術

アンテナを基板上に作るだけでなく、ICのパッケージ内部にアンテナを組み込む技術です。

配線長を極限まで短くできるため、損失を大幅に抑えることができます。

これにより、基板設計者はICそのものの実装精度にも配慮する必要が出てきています。

AIによる自動ルーティングと最適化

高周波設計の制約条件は非常に複雑で、人間が手作業ですべてを最適化するのは困難になりつつあります。

最新のEDA(設計支援ソフト)では、AIが何万通りものパターンをシミュレーションし、ノイズが最小になる配置を自動的に提案する機能が登場しています。

よくある質問(FAQ)

Q1:高周波設計において、なぜFR-4基板ではいけないのでしょうか?

FR-4は安価で加工しやすいですが、誘電正接(tanδ)が比較的大きいため、数GHzを超えると信号の減衰が激しくなります。

また、比誘電率のばらつきも大きいため、インピーダンスを厳密に管理する必要がある高周波回路には不向きです。

ただし、数GHz程度までであれば、設計の工夫次第でFR-4が使われることもあります。

Q2:ビアを打つと必ずノイズが増えるのでしょうか?

はい、基本的には増えると考えて間違いありません。

ビアは配線層を垂直に貫くため、そこでインピーダンスが乱れます。

また、ビアの壁面が小さなアンテナとなって放射ノイズを出すこともあります。

どうしても層を変える必要がある場合は、信号ビアのすぐそばにグラウンドビアを配置し、リターンパスを確保することが最優先事項です。

Q3:ガードリング(配線の周りを囲むグラウンド)は常に有効ですか?

必ずしもそうとは限りません。ガードリングと信号線の距離が近すぎると、逆に浮遊容量が増加し、信号波形をなまらせる原因になります。

また、ガードリングが適切にグラウンドに接地されていない場合、それがノイズを放射するアンテナとして機能してしまう逆効果もあります。

Q4:インピーダンス整合が取れているか、どうやって確認すればいいですか?

設計段階ではシミュレーターを使用しますが、実機ではネットワークアナライザという測定器を使用します。

Sパラメータ(S11:反射損失など)を測定し、スミスチャートと呼ばれる図表上でインピーダンスが中心(目標値)に集まっているかを確認します。

まとめ

高周波基板設計は、目に見えない電磁波との対話です。

ノイズを防ぐためのパターン配置において、最も重要なポイントを改めて整理します。

- インピーダンスの連続性を保つ:配線幅、角の形状、ビアの使用に細心の注意を払う。

- リターンパスを意識する:信号が通る道の真下には、必ず遮るもののないグラウンド面を用意する。

- 物理的な分離とシールド:ノイズ源とノイズに弱い部分を離し、適切にガードする。

- 適切な材料選定:周波数に見合った誘電損失の少ない基板材料を選ぶ。

これらは一見すると制約が多く、窮屈な設計に感じるかもしれません。

しかし、これらの原理原則を深く理解し、設計に落とし込むことができれば、手戻りのないスムーズな製品開発が可能になります。

技術の進歩とともに、高周波設計の難易度は今後も上がっていくでしょう。

しかし、本質的な「電磁波の振る舞い」は変わりません。

この記事で紹介した基礎とテクニックを土台にして、ぜひ高度な設計にチャレンジしてみてください。