現代の計算機科学において最もエキサイティングな領域の一つが量子コンピュータです。

中でも、IBMやGoogle、そして日本の理化学研究所などが採用している超伝導方式は、最も実用に近い有力候補として知られています。

しかし、量子コンピュータを語る際、多くの場合はアルゴリズムや量子ビットの数に注目が集まりがちです。

実際にそれらを動かすためには、絶対零度近くまで冷やされた極低温環境で動作する特殊な電子部品や、ナノ秒単位で制御を行う高度なエレクトロニクスが不可欠です。

この記事では、超伝導量子コンピュータを構成する部品群を、チップ内部の微細構造から室温の制御ラックまで、4つの階層に分けて網羅的に解説します。

製造現場での実装技術や調達の視点も含め、2026年現在の最新トレンドを詳細に紐解いていきましょう。

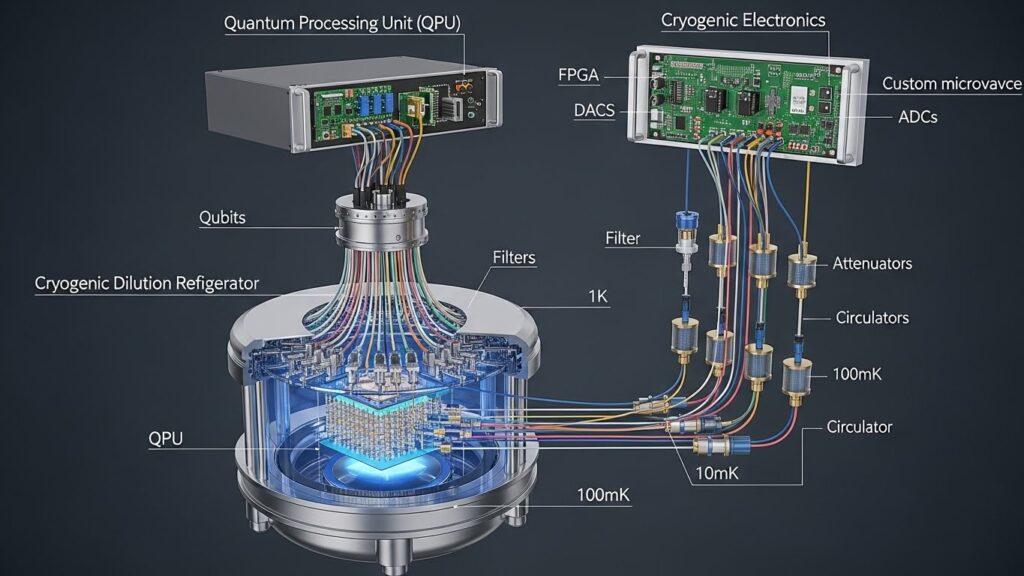

1. 超伝導量子コンピュータの階層構造と背景

量子コンピュータ、特に超伝導方式において最大の課題は、量子状態がいかに壊れやすいかという点にあります。

量子ビット(qubit)は外部からの熱、電磁波、磁場、さらには微細な振動によってもその状態を失ってしまいます。

これをデコヒーレンスと呼びます。

このデコヒーレンスを防ぎ、計算精度(フィデリティ)を高めるためには、ハードウェア全体を物理的に4つの階層で捉える必要があります。

- 量子プロセッサ(QPU)層:計算の核となる超伝導回路。

- 極低温信号伝達・フィルタ層:信号を送り届け、ノイズを遮断する血管。

- 受動部品・基板実装(SMT)層:極低温で動作を支えるディスクリート部品。

- 制御エレクトロニクス層:室温で量子操作を司る頭脳。

これらすべての層が完璧に調和して初めて、量子コンピュータは機能します。

特に超伝導方式では、量子プロセッサを 10mK (マイナス273.14℃)という、宇宙空間よりも低い温度に保つ必要があります。

この過酷な環境下で、いかに信頼性の高い電気信号のやり取りを行うかが、ハードウェアエンジニアリングの真髄です。

2. 量子計算を可能にするハードウェアの仕組み

超伝導量子コンピュータの心臓部は、電気抵抗がゼロになる超伝導現象を利用したLC回路の一種です。

しかし、通常のLC回路では、エネルギー準位が等間隔に並んでしまい、特定の2つの状態(0と1)だけを取り出すことができません。

ここで重要になるのが、ジョセフソン接合という素子です。

これは2つの超伝導体の間に極薄の絶縁体層を挟んだもので、非線形なインダクタンスを提供します。

これにより、エネルギー準位の間隔を不均等にし、特定のマイクロ波を照射することで 0 と 1 の状態間だけを遷移させることが可能になります。

読み出し(リードアウト)の際は、量子ビットに結合した読み出し共振器にマイクロ波を送り込み、その反射波の位相変化を観測します。

量子ビットが 0 のときと 1 のときで共振周波数がわずかにずれるため、反射波の位相を解析することで状態を判定します。

この微弱な信号を室温までノイズを乗せずに吸い上げることが、ハードウェア設計の最優先事項となります。

3. 第1層:量子プロセッサ(QPU)層

QPUは、シリコンやサファイアのウェハー上にナノメートル〜マイクロメートル単位の微細加工技術を用いて形成されます。

ジョセフソン接合 (Josephson Junction)

量子ビットの性能を左右する最重要部品です。

通常、アルミニウム(Al)と酸化アルミニウム(AlOx)の積層構造で作られます。

絶縁体層の厚さはわずか数ナノメートルであり、この厚さの均一性が量子ビットの周波数のばらつきに直結します。

現場の視点では、この接合部の酸化プロセスをいかに精密に制御するかが、チップの歩留まりを決定する最大の関門となります。

超伝導キャパシタ

量子ビットにエネルギーを蓄えるための部品です。

チップ上にニオブ(Nb)やタンタル(Ta)といった金属パッドを配置することで形成されます。

近年では、誘電体損(エネルギーが熱として逃げる現象)を抑えるために、非常に純度の高い金属膜の成膜技術が求められています。

読み出し共振器 (Readout Resonator)

特定の周波数のマイクロ波に反応するよう設計された、チップ上の伝送路です。

量子ビットの状態を外部へ伝えるアンテナの役割を果たします。

ここでの設計ミスは信号の減衰やクロストーク(隣接するビットへの干渉)を招くため、高度な電磁界シミュレーションに基づいたレイアウト設計が行われます。

4. 第2層:極低温信号伝達・フィルタ層

希釈冷凍機(Dilution Refrigerator)の内部は、室温から10mkまで段階的に温度が下がっています。

この温度勾配を維持しながら、高速な電気信号を通すための部材が必要です。

極低温用部材の特性一覧

| カテゴリ | 具体的な部品・部材 | 役割と物理的特性 |

| 同軸ケーブル | NbTi(ニオブチタン)セミリジッドケーブル | 超伝導材を使用し、電気抵抗をゼロに、かつ熱伝導を極限まで抑える。 |

| コネクタ | 非磁性SMA / SMPコネクタ | ベリリウム銅などを使用。磁性体(ニッケル等)は超伝導を壊すため厳禁。 |

| アッテネータ | 固定減衰器(極低温仕様) | 室温からの熱雑音(ジョンソンノイズ)を削ぎ落とすために、各温度ステージに配置。 |

| フィルタ | 赤外線(IR)フィルタ | 量子ビットのエネルギーを奪う高周波の赤外線輻射を物理的に遮断する。 |

| 増幅器 | HEMT増幅器 / JPA | ステージで信号を増幅。JPA(量子制限増幅器)はノイズを極限まで抑えた超高性能増幅器。 |

| アイソレータ | 極低温用サーキュレータ | 信号を一方通行にし、増幅器からの逆流ノイズが量子ビットに届くのを防ぐ。 |

特に同軸ケーブルの選定は重要です。

通常の銅ケーブルは熱を非常によく伝えるため、冷凍機の冷却能力を上回る熱を室温から持ち込んでしまいます。

そのため、低温部では熱伝導率の低いステンレス鋼や超伝導体のニオブチタンを用いたケーブルが使い分けられます。

5. 第3層:受動部品・基板実装(SMT)層

QPUを搭載するパッケージ基板や、その周辺に配置される受動部品には、家庭用電化製品とは全く異なるスペックが要求されます。

コンデンサ (Capacitors)

一般的な積層セラミックコンデンサ(MLCC)の多くは、極低温で容量が激減したり、誘電損失が大きくなったりします。

そのため、温度変化に対する容量変化が極めて小さいC0G(NP0)特性のセラミックコンデンサや、高周波特性に優れた薄膜コンデンサが厳選されます。

抵抗器 (Resistors)

炭素皮膜抵抗は低温で抵抗値が数倍〜数十倍に跳ね上がる特性を持つため使用できません。

ニッケルクロムなどの合金を用いた金属皮膜チップ抵抗、特に温度係数(TCR)が極めて小さい薄膜抵抗が採用されます。

基板(PCB)と実装技術

一般的なFR-4基板は、樹脂の誘電損失が大きいため、マイクロ波信号を扱う量子コンピュータには不向きです。

テフロン基板やセラミック基板といった、高周波特性に優れた素材が使われます。

また、表面処理にも細心の注意が必要です。

一般的な「無電解ニッケル金メッキ(ENIG)」に含まれるニッケルは強磁性体であり、これが量子ビットの近くにあると磁場を乱し、コヒーレンス時間を著しく悪化させます。

そのため、ニッケルを含まない「厚付け銅」や「純金メッキ」が指定されます。

ハンダ付けについても、極低温での熱収縮(熱膨張係数の差)によるクラック(ひび割れ)が大きなリスクとなります。

これを防ぐために、インジウム(In)などの柔らかい金属を用いた圧着や、特殊な鉛フリーハンダが検討されます。

6. 第4層:制御エレクトロニクス層

冷凍機の外にある室温環境には、量子ビットを操作するための膨大なエレクトロニクスが並んでいます。

これらは主に19インチラックに収められた高精度な計測機器群です。

FPGAボード

Xilinx Zynq UltraScale+ などの高性能なFPGA(Field Programmable Gate Array)が中心的な役割を担います。

量子計算では、読み出した結果に基づいてナノ秒単位で次の操作を決定する「フィードバック制御」が必要なため、極めて低いレイテンシ(遅延)が求められます。

高速DAC / ADC

デジタル信号をアナログのマイクロ波パルスに変換するDAC(D/Aコンバータ)と、反射波をデジタル化するADC(A/Dコンバータ)です。

サンプリングレートは数GHzから十数GHzに達し、ジッタ(時間の揺らぎ)を極限まで抑えたクロック同期が必要です。

I/QミキサーとDC電源

FPGAで生成したベースバンド信号を、量子ビットの操作周波数( 4~8Ghz )へアップコンバートするためにI/Qミキサーが使用されます。

また、量子ビットの周波数を微調整するために、超伝導回路に微弱な磁場をかけるための、極めてノイズの少ない精密DC電源も欠かせません。

7. 作業の具体的な流れ:量子システムの実装ステップ

量子コンピュータのハードウェアを構築する際、技術者がどのようなステップを踏むのか、具体的に見ていきましょう。

ステップ1:チップの設計とクリーンルームでの製造

QPUの回路図を作成し、電子ビームリソグラフィなどの装置を用いてウェハー上に回路を形成します。

ジョセフソン接合の臨界電流値を精密に合わせ込むため、製造途中で何度も電気特性のチェックを行います。

ステップ2:コンポーネントの極低温スクリーニング

使用する抵抗、コンデンサ、ケーブル、コネクタが、実際に10mkでスペック通りの性能を出すか、事前に液体ヘリウムなどを用いた極低温テストで選別(スクリーニング)します。

ステップ3:パッケージングと配線

QPUを専用のパッケージに収め、超伝導バンプやワイヤボンディングで接続します。

その後、希釈冷凍機の各温度ステージにアッテネータやフィルタを配置しながら、数十本におよぶ同軸ケーブルを手作業で丁寧に配線していきます。

ステップ4:冷却と真空引き

冷凍機の内部を高度に真空引きした後、数日かけて徐々に冷却します。

( 4~8Ghz )付近でパルス管冷凍機を動かし、最終的に希釈サイクルを回して 10mkを目指します。

この過程で配線が断線したり、ネジが緩んだりしないよう、事前のトルク管理が徹底されます。

ステップ5:システムキャリブレーション

温度が安定したら、室温のエレクトロニクスからパルスを送り、量子ビットの共振周波数を探します。

Rabi振動の観測、T1(エネルギー緩和時間)、 T2 (位相緩和時間)の測定を行い、各ビットの特性をデータベース化して制御ソフトウェアに反映させます。

8. 2026年現在の技術トレンドと将来性

量子ビット数が増加するにつれ、現在の「1ビットに対して数本の同軸ケーブルを引く」という手法は物理的な限界(ワイヤリング・ボトルネック)に直面しています。

3D実装と垂直配線

チップの側面から配線を取り出すのではなく、チップの裏側から信号を通すTSV(Through Silicon Via:シリコン貫通電極)や、マイクロバンプを用いたフリップチップ実装が主流になりつつあります。

これにより、チップ中央部に配置された量子ビットにも直接アクセスが可能になり、スケーラビリティが飛躍的に向上します。

極低温制御IC (Cryo-CMOS)

これまで室温にあったFPGAやDACの機能の一部を、冷凍機内部の 4Kステージに配置するための研究が進んでいます。

これを「Cryo-CMOS」と呼びます。

室温から伸ばすケーブルを最小限にし、冷凍機内部で多重化・信号処理を行うことで、配線の物量を劇的に削減することを目指しています。

超伝導ハンダと新素材

実装現場では、磁性を排除しつつ熱サイクルに耐える接合技術として、インジウムバンプの他に、新しい超伝導ハンダ組成の開発が進んでいます。

また、誘電損失をさらに下げるために、基板材料として合成サファイアや高抵抗シリコンの採用が拡大しています。

9. よくある質問(FAQ)

Q1:なぜ銀や銅などの良導体を配線に使い続けないのですか?

銀や銅は電気をよく通しますが、同時に熱も非常によく伝えてしまいます。

室温(300K)から 10mK への熱流入を抑えるためには、あえて電気抵抗がある程度あり熱を伝えにくいステンレス鋼や、特定の温度以下で熱伝導が急激に下がる超伝導材料(NbTiなど)を使う必要があるからです。

Q2:磁性体がなぜ量子ビットに悪影響を与えるのですか?

超伝導状態は非常に繊細な磁場環境に依存しています。

磁性体(ニッケルなど)が近くにあると、意図しない局所的な磁場が発生し、量子ビットのエネルギー準位を揺らしてしまいます。

これが計算エラーの大きな原因となるため、部品やメッキには非磁性体が厳格に求められます。

Q3: $10\,mK$ まで冷やすのにどのくらいの時間がかかりますか?

装置のサイズにもよりますが、室温から 10mKまでの冷却には通常24時間から3日程度かかります。

特に 4K から 10mK への最終段階は、ヘリウム3とヘリウム4の混合液を用いた物理的な熱交換プロセスが必要で、慎重な制御が求められます。

10. まとめ

量子コンピュータの実現は、単なる理論物理の勝利ではなく、極限環境における精密なエンジニアリングの集大成です。

QPU層での微細なジョセフソン接合、極低温層での熱と信号のトレードオフを解消する配線技術、SMT層での磁性を排除した特殊実装、そして室温層での高速フィードバック回路。

これら4つの階層における電子部品の一つひとつが、量子という繊細な世界を支える礎となっています。

今後、量子ビット数が数百、数千と増えていく過程で、3D実装やCryo-CMOSといった次世代技術がさらに重要性を増していくでしょう。

製造現場や調達の視点から見れば、これらの特殊な要求に応えられる部品メーカーや実装技術を持つ企業の存在こそが、量子コンピュータの実用化を加速させる鍵となります。

次世代のコンピューティング基盤を支えるのは、こうした目に見えない場所で動作する、極低温の電子部品たちなのです。